Esoterica: Next-gen x64 Cores and Micro-op Caches

Are micro-op caches going away or not?

Most of the time on Computer Enhance I try to post information I think subscribers want to know. I’m sure I don’t always hit the mark, but that’s what I’m trying to do.

This post, I’m afraid to say, is the opposite of that. I’m guessing very few of you will care about this, but, I wanted to gather the information for my own edification, and I figured it couldn’t hurt to share it with those (few) subscribers who might be interested.

To avoid distracting you with highly niche posts like this one, I’ve tried to distinguish it by labeling it “Esoterica”, a convention I will use from now on anytime I post something of obviously marginal interest. This way, any time you see “Esoterica:” in your inbox, you can tell right from the title it’s going to be an “off in the weeds” post from me.

OK, with that out of the way:

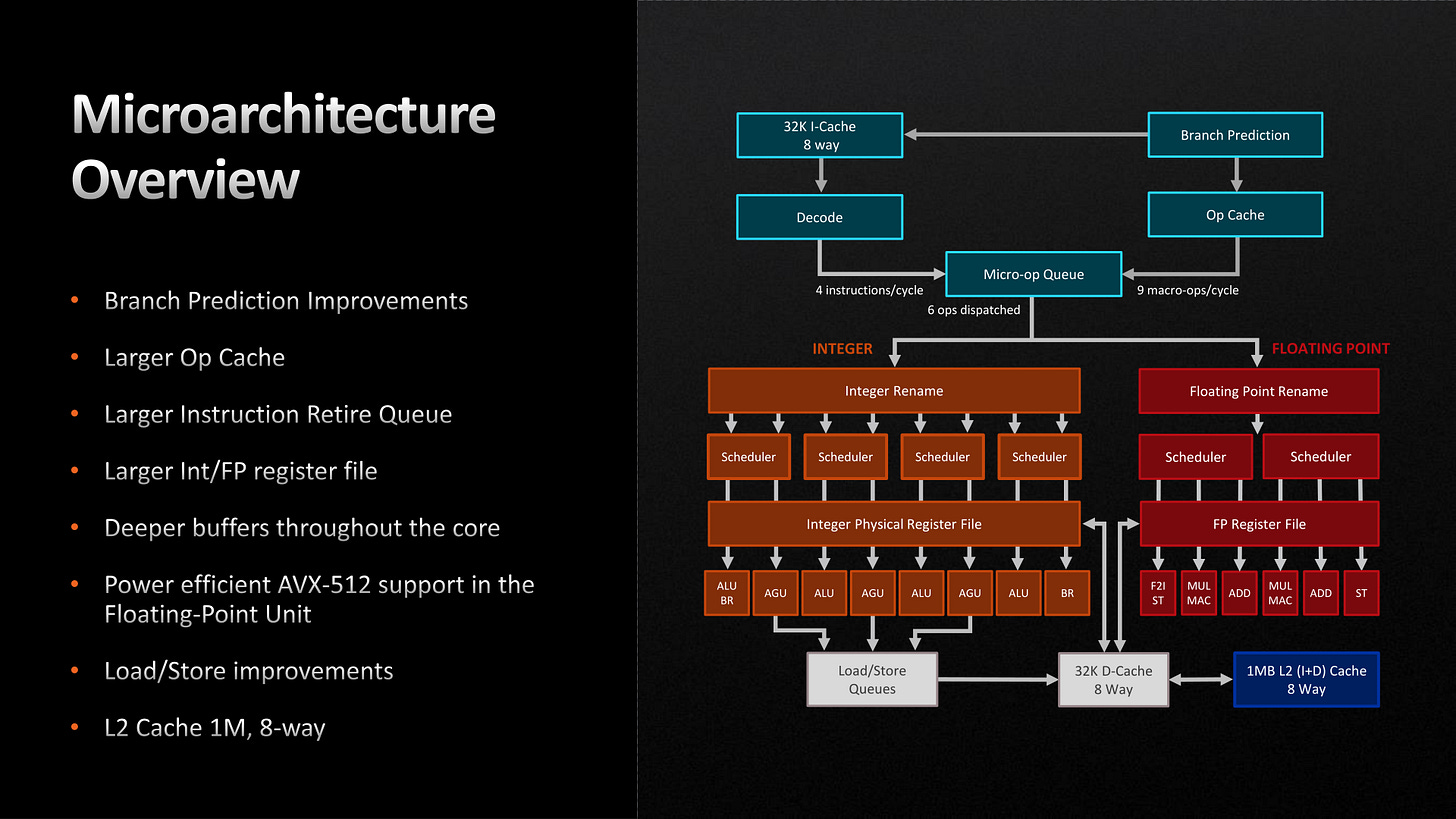

Recently I was asked to give a walkthrough of microarchitecture basics on the Off By One Security YouTube channel. I showed the kinds of diagrams we often cover here on Computer Enhance, like this flowchart from AMD’s Zen 4 presentation:

While I was going over the diagram, I mentioned the box labeled “Op Cache” and explained that it was a cache for micro-ops (uops) that had previously been decoded (as we encountered in the Code Alignment video from the Performance-Aware Programming series, for example).

I also mentioned in passing that it might be “going away” in future architectures like Zen 5. This was purely speculative, of course, and it was based on a rumor I had heard privately from another software developer.

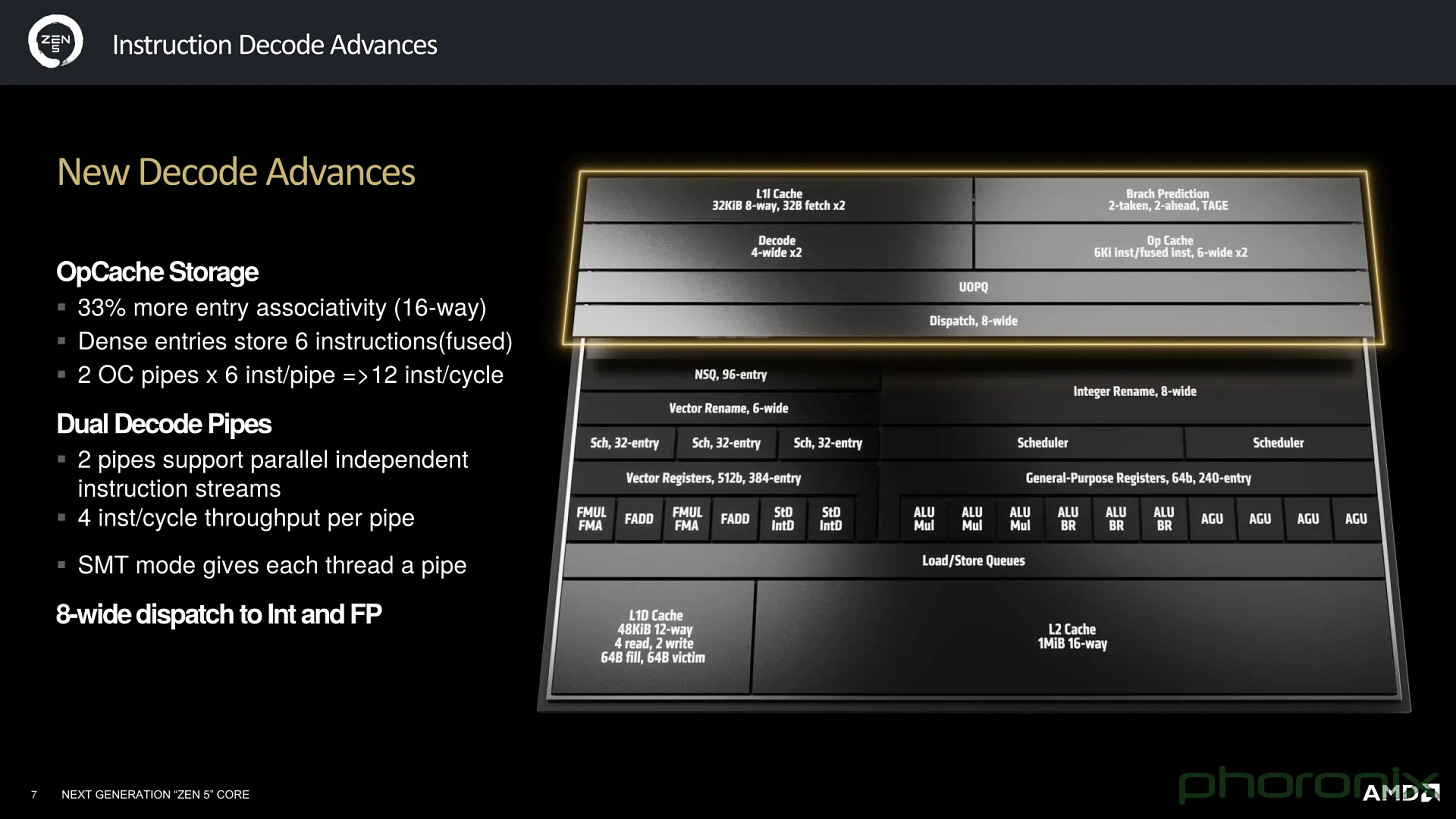

After the stream was over, however, I just so happened to open Chips and Cheese to check if there was a new article to read. There was, and as luck would have it, it contained a partial Zen 5 block diagram:

As you can see from the middle-left of the diagram, the “Op Cache” does not appear to have “gone away” at all! It’s right there like you would expect.

Now, Chips and Cheese is an excellent site, but of course, everyone makes mistakes. So I figured I’d double-check to see if AMD had released official documentation on the Zen 5 to confirm this. As it turns out, just two days ago they released Zen 5 details that cover the Zen 5 op cache:

According to their slide presentation, not only is the uop cache not going away, it’s getting more powerful!

This made me think, well, I might be misremembering the rumor. Perhaps it was only Intel who was getting rid of uop caching, so it’s expected that Zen 5 would still have it. I went ahead and looked up Intel’s latest presentation on their upcoming Lion’s Cove core to see if they mentioned it:

Plenty of uop cache in Lion’s Cove, just like Zen 5!

So that pretty much nails the coffin shut on the rumor. Unless it was about the next next-gen cores — like Zen 6 or beyond — it’s clearly false.

For completeness, it is worth noting that Intel’s upcoming Skymont “efficiency” core does not appear to have a uop cache. If you look at Intel’s Skymont slide presentation, it is absent from the architecture diagrams.

However, that doesn’t vindicate the rumor, because as far as I know, the E-cores never had uop caches to begin with.

As I always say, I’m not a hardware guy, so I could be wrong about that. But, to the best of my knowledge, neither Goldmont, Tremont, Gracement, nor Crestmont had uop caches. It can hardly save the rumor to claim that it was about E-cores, since the uop cache can’t “go away” if it was never there to begin with!

So that about wraps it up for this esoteric note. There doesn’t appear to be any shift in the CPU zeitgeist away from uop caches, at least as far as the high-performance cores are concerned. There’s always the next next gen, and I’ll be sure to keep an eye out for changes there. But for now, the uop cache seems to be alive and well in both AMD’s and Intel’s high-performance x64 core designs.

Thank you for introducing to Chips and Cheese website. Plenty of awesome reading to be done there.

Esoteric or not thats why we are here, keep them coming and thanks!